Press release

Related Press

12 June 2025

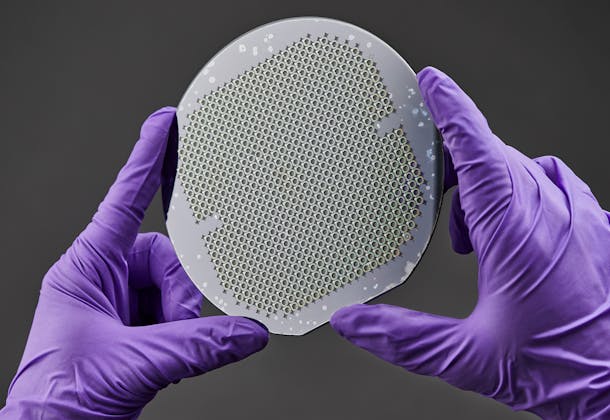

GENESIS project launches to lead Europe’s transition to sustainable semiconductor manufacturing

CSEM is part of the EU-funded GENESIS project to drive sustainable innovation in semiconductor manufacturing with advanced sensing, green materials, and PFAS-free processes....

27 June 2022

New miniature atomic watches will soon hit the market

The EU-funded macQsimal project, coordinated by CSEM as part of the EU's FET Flagship on Quantum Technologies program, has now drawn to a close, after leading to some promising discoveries. ...

10 March 2021

Victory for Gait Up and Definition12

CSEM has announced the two winners of its 2020 Digital Journey award: Gait Up, based in Renens in the Canton of Vaud, and Definition12, based in Reinach in the Canton of Basel-Landschaft....