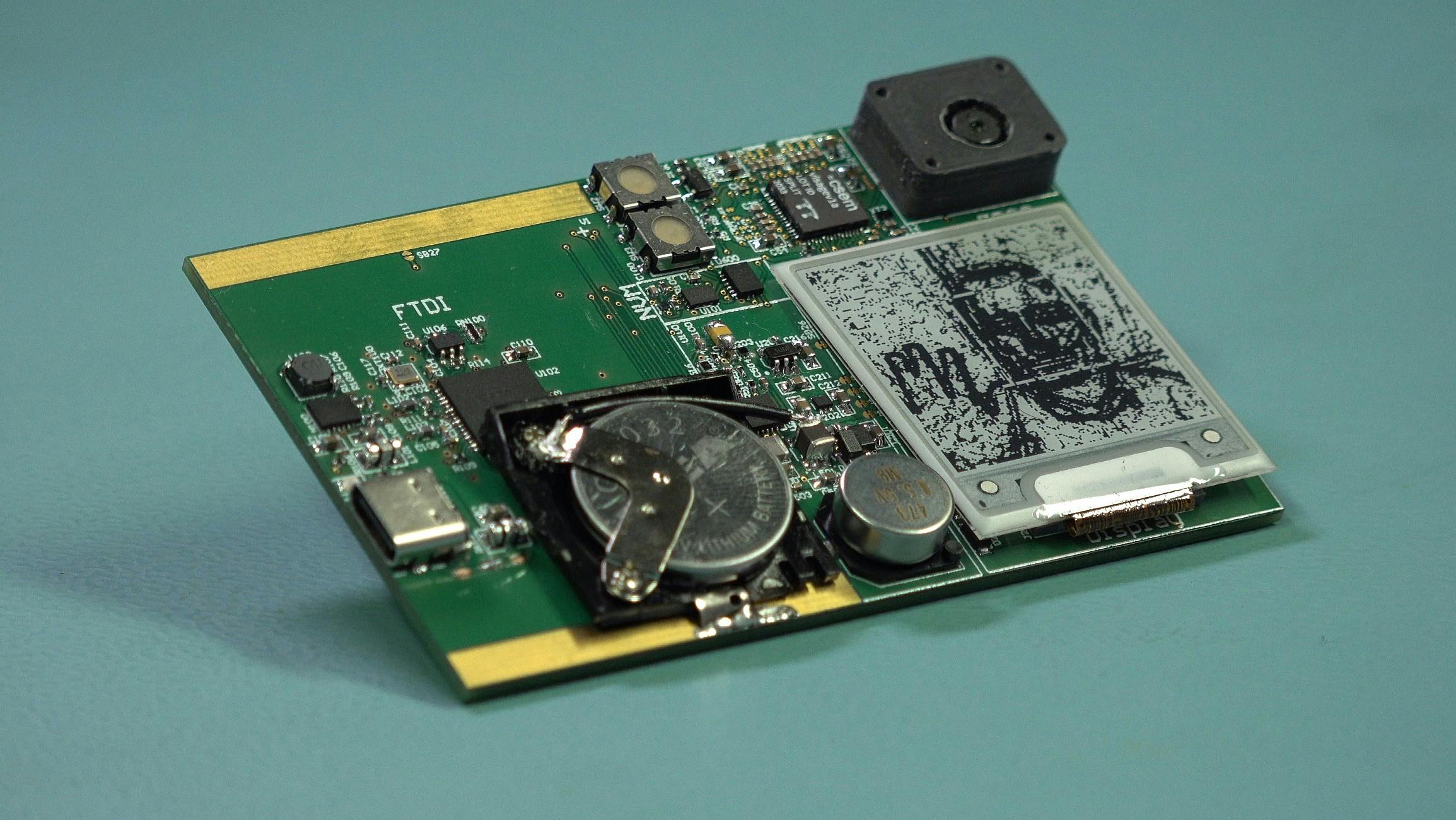

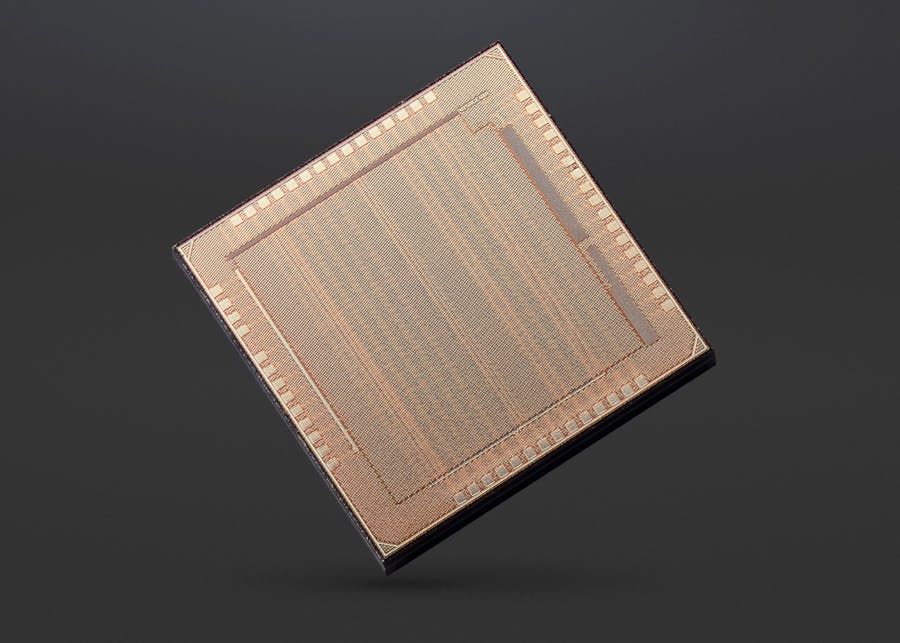

The CSEM system-on-chip works through an entirely new signal processing architecture that minimizes the amount of power needed. It consists of an ASIC chip with a RISC-V processor (also developed at CSEM) and two tightly coupled machine-learning accelerators: one for face detection, for example, and one for classification. The first is a binary decision tree (BDT) engine that can perform simple tasks but cannot carry out recognition operations.

The second accelerator is a convolutional neural network (CNN) engine that can perform these more complicated tasks – recognizing individual faces and detecting specific words – but it also consumes more energy. This two-tiered data processing approach drastically reduces the system’s power requirement, since most of the time only the first accelerator is running.

As part of their research, the engineers enhanced the performance of the accelerators themselves, making them adaptable to any application where time-based signal and image processing is needed.