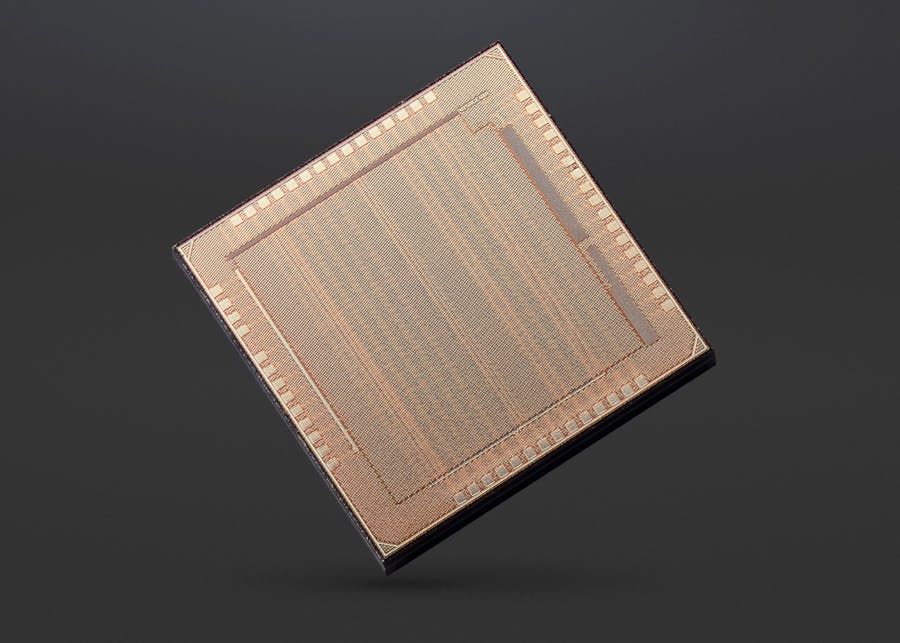

Pour parvenir à ce résultat, les scientifiques ont innové dans la façon de procéder à l’analyse des signaux, afin de réduire au maximum la consommation d’énergie. La puce (ASIC) contient ainsi un processeur (RISC-V, également développé au CSEM), gérant deux accélérateurs, en charge de la reconnaissance et de la classification. Le premier est un accélérateur BDT (Binary Decision Tree), consommant très peu d’énergie et capable de réaliser des tâches simples, mais pas la reconnaissance en elle-même.

Si la réponse aux premières questions est oui, le second accélérateur, de type CNN (Convolutional Neural Network), est alors enclenché. Un peu plus énergivore, il gère les tâches complexes et pourra ainsi reconnaître les visages ou discerner les mots. Grâce à ce fonctionnement d’analyse hiérarchisée, le besoin en énergie du système est ainsi très faible, puisque seul le premier accélérateur est généralement allumé.

Les chercheurs ont également utilisé leur expérience pour optimiser les accélérateurs eux-mêmes, et surtout les rendre adaptables à toute sorte d’applications basées sur l’analyse d’images ou de signaux variant avec le temps.