Pressemitteilung

Ähnliche Medienmitteilungen

25. February 2025

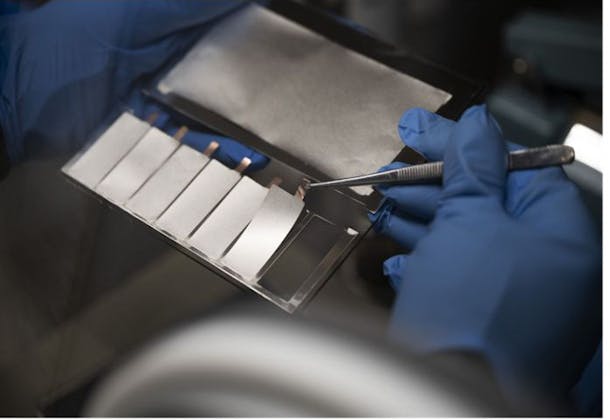

CSEM eröffnet ersten Schweizer Trockenraum und beschleunigt so die Batterieinnovation

CSEM eröffnet die erste Trockenraum-Anlage der Schweiz, um die Innovation bei Batterien der nächsten Generation zu beschleunigen. Mit einem extrem niedrigen Taupunkt (-50 °C) und einer Pilotlinie für ...

8. June 2022

Bewerbungsstart für KMU

Zum fünften Mal startet CSEM seinen Wettbewerb «CSEM Digital Journey», der explizit für Schweizer KMU entwickelt wurde. ...

19. August 2020

Intelligente Steuerung für das Management erneuerbarer Energien

Le CSEM a mis au point une plateforme intelligente capable de gérer et planifier la production et la consommation d’énergies renouvelables à l’échelle de tout un quartier....