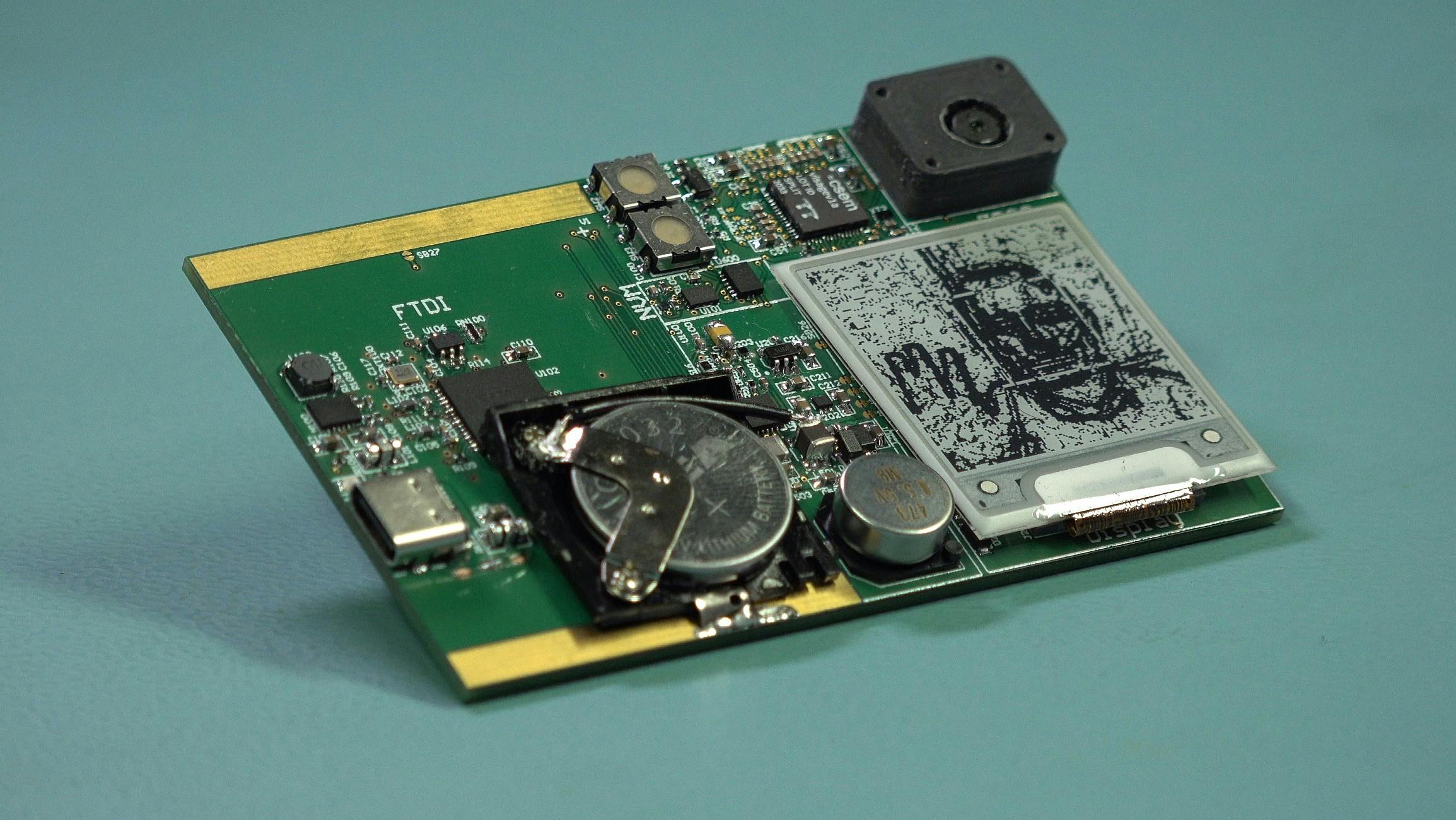

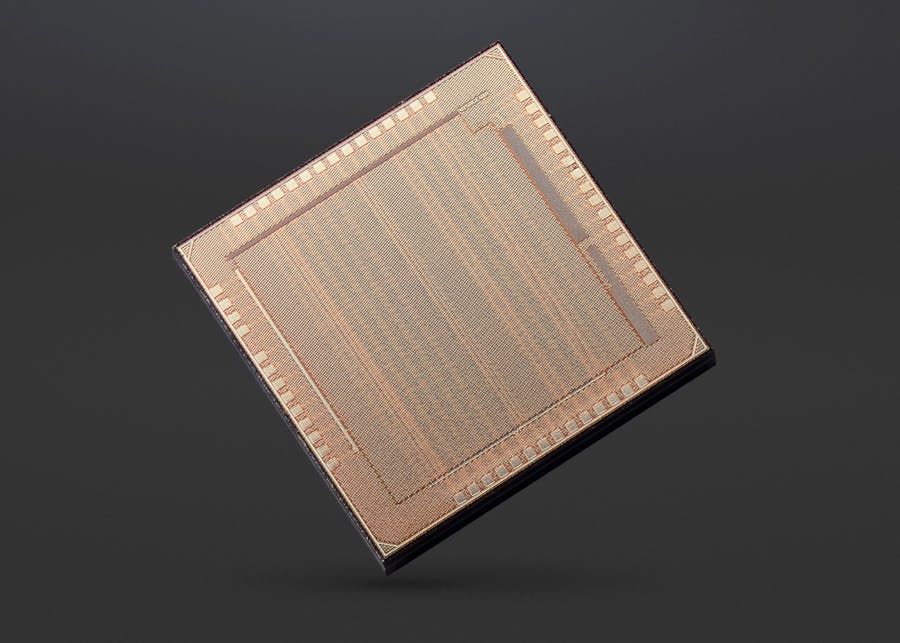

Die Wissenschaftlerinnen und Wissenschaftler haben eine neue Art der Signalanalyse entwickelt, um den Energieverbrauch so weit wie möglich zu reduzieren. Der Chip (ASIC) enthält einen beim CSEM entwickelten Prozessor (RISC-V), der zwei Beschleuniger steuert, die für die Erkennung und Klassifizierung zuständig sind. Der erste ist ein BDT-Beschleuniger (BDT: Binary Decision Tree), der sehr wenig Energie verbraucht und in der Lage ist, einfache Aufgaben, nicht aber die Erkennung selbst zu übernehmen.

Nur wenn die ersten Fragen mit Ja beantwortet werden, wird der zweite Beschleuniger vom Typ CNN (Convolutional Neural Network) aktiviert. Er verbraucht zwar etwas mehr Energie, bewältigt dafür aber komplexe Aufgaben und ist in der Lage, Gesichter zu erkennen oder Wörter zu unterscheiden. Dank dieser hierarchisch gestalteten Analyse ist der Energiebedarf des Systems sehr gering, da meistens nur der erste Beschleuniger eingeschaltet ist.

Die Forscherinnen und Forscher nutzten zudem ihre Erfahrung, um die Beschleuniger selbst zu optimieren und vor allem, um sie so zu konzipieren, dass sie an alle Arten von Applikationen, die auf der Analyse von Bildern oder zeitlich veränderlichen Signalen basieren, angepasst werden können.