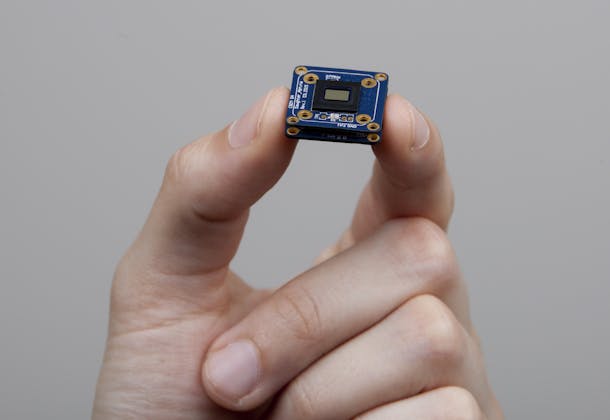

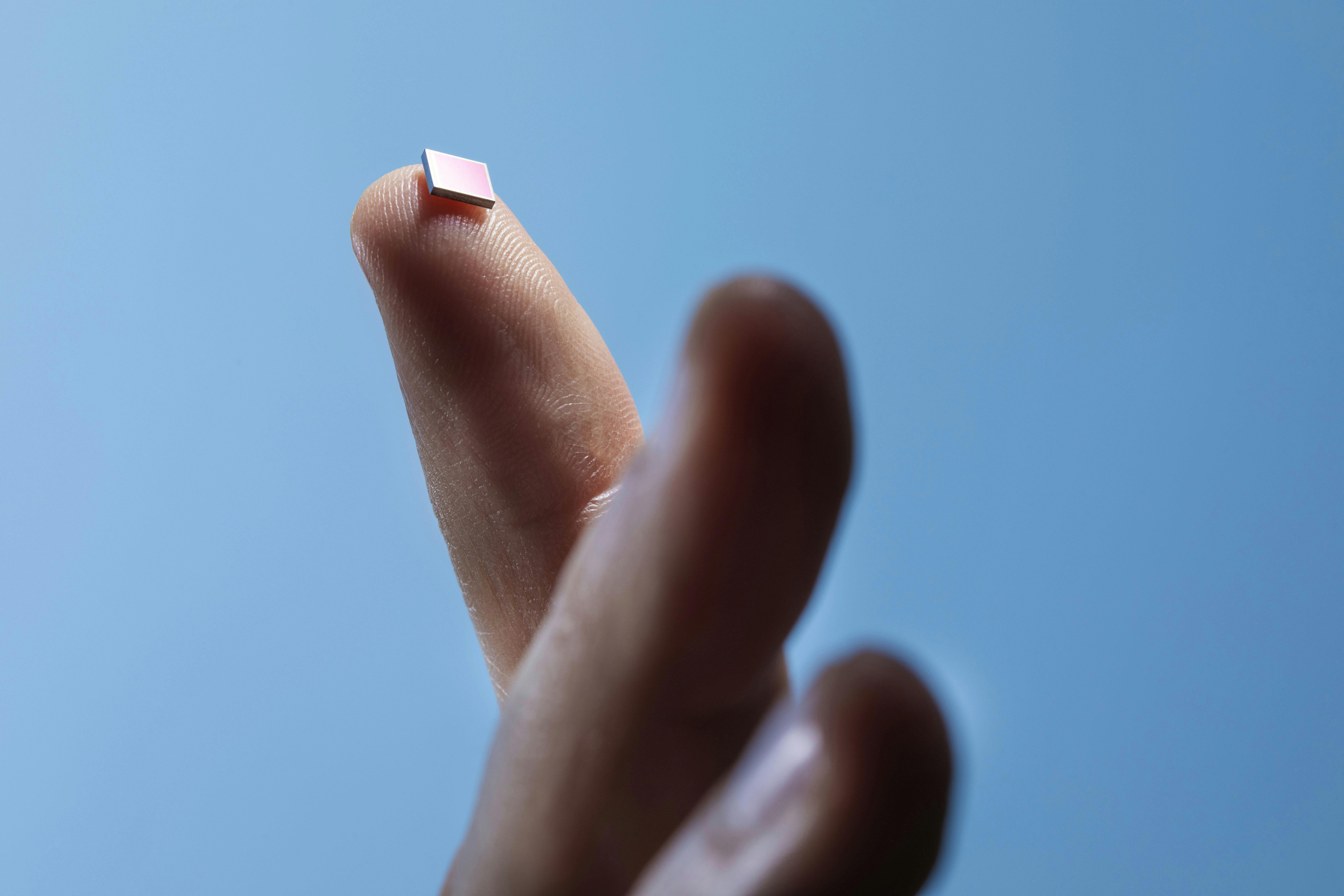

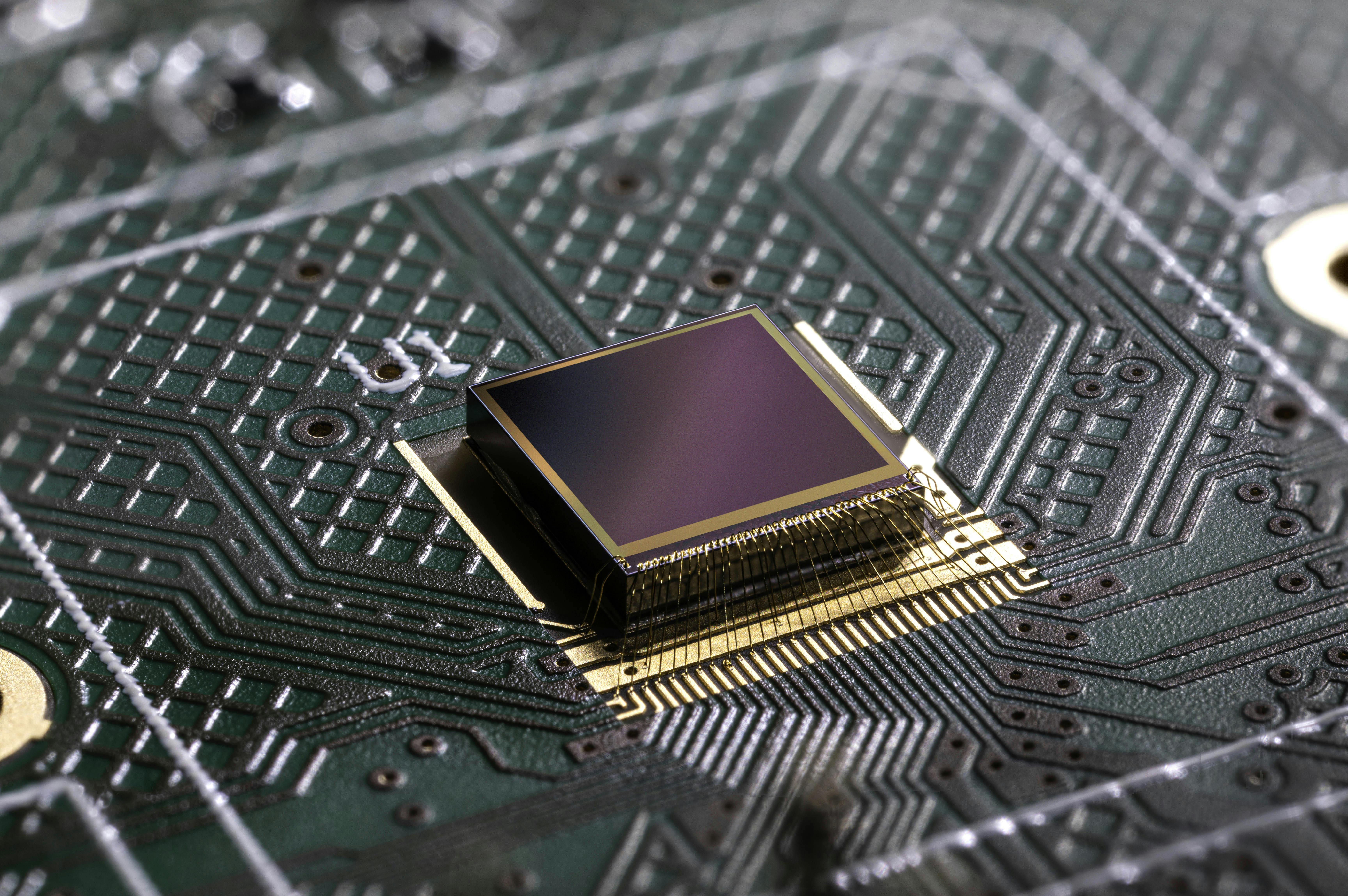

Our uniquely designed systems-on-chips with sensor interfaces, communication, and hardware will power your edge computing needs, providing real-time, low-latency and privacy-preserved insights into your data. Ultra-low-power (ULP) ASIC, SOC design services and silicon IPs are combined with sensor interfaces, imagers, ADC, MCU, and ML-derived hardware accelerators, wireless communication, ranging or localization circuits that can be co-integrated with power management and energy harvesting units.

This delivers always-on, battery-less, energy-autonomous, unobtrusive smart-sensing systems. Our USP is our ULP: custom hardware and ASICs, which achieve a 10x reduction in power consumption courtesy of architectural innovation.