## Fully Integrated Low-power Bio-potential Acquisition Analog Front-end IC

M. Augustyniak, Y. Zha, J. Deng, A. Bischof, M. Pons Solé, C. Monneron, R. Godinho Caseiro, S. Emery

A highly reconfigurable, ultra-low power, 20-channel system-on-a-chip (SoC) for biomedical signal acquisition is presented. It is designed to acquire electro-encephalo, -cardio and -myogram (ExG) signals having an amplitude spanning from 1  $\mu$ V to 10 mV in a frequency range from sub-Hz to 10 kHz.

Personalized healthcare solutions for 24/7 monitoring of an aging but connected population hold the promises to move the point of care from hospitals to the home reducing costs.

To meet that goal, low-cost, miniaturized, lightweight and unobtrusive wearable or implantable systems able to measure and monitor vital signs have to be developed to improve patients comfort and ease adoption. System-on-chips have a great potential to fulfill the above requirements by co-integrating sensing, data processing and transmission functions on a single miniature die that can be mass-produced at low cost.

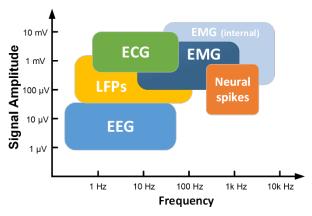

A variety of physiological signals can be recorded with electrode-based measurements such as EEG, ECG and EMG, hence potentially with a single, generic ExG monitoring circuit. However, high reconfigurability is required to acquire such various electrical signals having voltages spanning from 1  $\mu V$  to 10 mV in a frequency range from sub-Hz to 10 kHz as illustrated in Figure 1.

Figure 1: Physiological signals recording: frequency and voltage range.

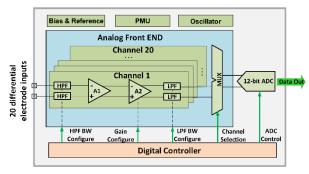

Figure 2 shows the architecture of a circuit designed to meet such challenges. Featuring twenty ultra-low power parallel channels, the Analog-Front-End (AFE) that is configured digitally performs tailored filtering and amplification depending on the type of signals being recorded. Channels are then multiplexed before optimally amplified signals are digitized sequentially at a rate of 1 MSPS with a  $\pm 0.9$  V full scale 12-bit SAR ADC.

Figure 2: Block diagram of the 20-channel bio-potential acquisition system.

There are several design challenges associated with the acquisition of such signals. Firstly, the contact between electrode and skin is a metal-to-electrolyte interface, which superimposes a DC half-cell potential to the biomedical signal of interest. It results in a time-varying offset voltage which can exceed the tiny signal amplitude by more than four orders of magnitude. This requires a high-gain, low-noise AFE which is robust to differential offset drift and has a high input impedance and high Common-Mode Rejection Ratio (CMRR).

Another major challenge is the trade-off between power, noise, linearity, area and the input impedance. Considering these difficulties, an RC High-Pass Filter (HPF) is implemented using a temperature compensated pseudo resistor and on-chip capacitor. A two-stage amplification path is used with a proper optimized value of the input transistor size for obtaining higher gain, linearity, output swing, while achieving lower noise and consuming less power. Each amplifier has a configurable high-pass-filter characteristic for offset elimination, high CMRR (ca. 85 dB) and noise filtering. A Chebyshev gm-C low-pass filter (LPF) with on-the-fly autonomous calibration is implemented for band limitation and further noise reduction.

In order to perform on-chip processing of the digitized data so as to e.g., suppress motion-induced artefacts or extract higher level features for surveillance, a pre-processing accelerator complemented with a 32 b icyflex2 RISC processor, 256 kB SRAM, 64 kB ROM, a programmable sequencer, 8 timers, 16 GPIOs, I<sup>2</sup>C, SPI, JTAG, UART) are co-integrated forming a compact vital sign monitoring SoC suitable for applications based on ExG measurements.

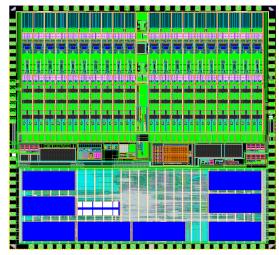

The AFE consumes only 24  $\mu$ W per channel while maintaining large gain and bandwidth configurability. The MCU and accelerators are designed to run at 150 MHz. A picture of the layout of the SoC, which is currently being manufactured, is shown in Figure 3.

Figure 3: Layout of the SoC designed for ExG signal acquisition applications.